Die ETH Zürich ist bekannt für ihre vielfältigen RISC-V-Designs, aber der Manticore sticht heraus: Der nach dem persischen Fabelwesen benannte Prozessor verfügt über 4.096 Kerne und ist für Gleitkommaberechnungen mit besonders hoher Effizienz ausgelegt. Die Forscher präsentierten den Manticore auf der jährlichen Hot Chips-Technologiekonferenz und zeigten die ersten Leistungswerte basierend auf einem Prototyp.

Stellenmarkt

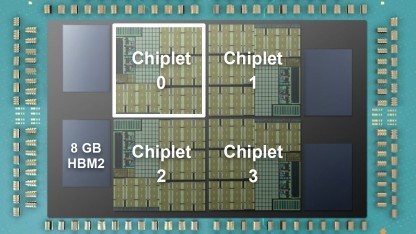

Manticore wird später aus vier miteinander verbundenen Chips bestehen, von denen jeder Zugriff auf seinen eigenen 8-GB-HBM2-Stack hat. Für die Herstellung der Formen will die ETH Zürich das 22FDX-Verfahren von Globalfoundries nutzen, die geplante Oberfläche pro Chip beträgt knapp 222 mm². Intern besteht jeder Chip aus einer HBM2- und einer PCIe Gen3 x16-Schnittstelle, vier Ariane RV64G-Kernen für ein Linux-Betriebssystem, einem vollständigen 27 MB L2-Cache und vier Quadranten.

Diese Quadranten enthalten die tatsächliche Rechenleistung, da jeder aus 32 Clustern mit jeweils 8 Kernen besteht. Die ETH Zürich verwendet die selbst entworfenen Schnatzkerne (PDF): Dies sind kleine RV32G-Kerne mit wenig Steuerlogik und einer zusätzlichen Gleitkommaeinheit, mit denen das Stream Semantic Register (SSR) und ein Floating Point Repetition Instruction (FREP) die Effizienz steigern können. Jeder Schnatzkern erzeugt 32 FP- und 16 DP-Flops pro Zyklus. FP8, Bfloat und F16 werden ebenfalls unterstützt. Insgesamt sollte der Manticore mehr als 27 Teraflops mit doppelter Präzision (FP64) produzieren.

Präsentation des Manticore-Designs (Bild: ETH Zürich)

Für die ersten Tests ließ die ETH Zürich einen 9 mm² großen Mantikor-Prototyp mit 22FDX-Produktion bauen. Es enthält 24 Snitch-Kerne und zwei Ariane-Kerne sowie einen 1,25 MByte L2-Cache. Das reicht für gute 54 Gflops mit FP64 bei über 1 GHz und 188 Gflops pro Watt bei etwa 500 MHz.

So verwaltet sich der Manticore in Bezug auf Effizienz Nvidias Tesla A100 leicht zu ziehen. Es ist zu beachten, dass der Manticore ein 22FDX-Design ist und Nvidia den GA100-Chip des Tesla A100 mit dem N7 von TSMC herstellte. In FP32-Berechnungen für tiefes neuronales Netzwerktraining wie Alexnet, Googlenet oder Resnet zieht der Manticore mit dem Älteren Tesla V100 Gleich.

Der nächste Schritt ist eine Leiterplatte mit vier Prototyp-Chipsätzen. Das Design soll unter Verwendung eines modernen und teureren Finfet-Herstellungsverfahrens hergestellt werden. Die ETH Zürich möchte auch Partner finden, die bei der Integration einer physischen Schnittstelle für DDR- oder HBM-Speicher helfen können. In der Frage-und-Antwort-Sitzung stellten die Forscher jedoch fest, dass es für die Universität schwierig war, auf SoC-Komponenten wie Interconnects zuzugreifen.

Umfangreiche Informationen zum offene Befehlssatzarchitektur RISC-V Wir haben in einem separaten Artikel zusammengefasst.

Oder benutze das Pures Golemangebot

und lies Golem.de

- ohne Werbung

- mit deaktiviertem JavaScript

- mit RSS-Feed für Volltext

Organisator. Schöpfer. Evangelist der lebenslangen Popkultur. Freundlicher Zombie-Praktizierender.

You may also like

-

5 Dinge über KI, die Sie heute vielleicht übersehen haben: Nachrichtenverlage werden KI-Unternehmen verklagen; Die Polizei setzt auf KI und mehr

-

Optimiere deine Online-Präsenz mit professioneller SEO-Beratung

-

Allwyn gibt erste Partnerschaft mit der prestigeträchtigen Peace Race Cycling Tour bekannt

-

dynaCERT gibt weltweite Verkäufe für Q4 2022 bekannt

-

Die Final Fantasy Pixel Remaster-Serie kommt für PS4, Switch Frühjahr 2023